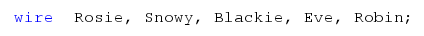

wireEvery circuit contains wires of some form if you're going to write code for your computer to form a circuit, you need to give your wires names so your computer knows which wire to put where. Please declare your wires by giving them names. Input and output wires are exception. You will name them in the paranthesis of a module. |

|

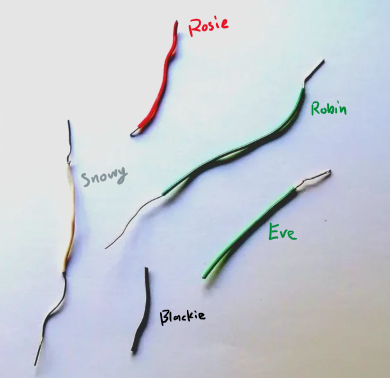

Default ModulesHere are some default modules you can use When using a module, please instantiate to give it a name and purpose in life. Type the gate you're using (e.g. and, or, not, nand) and type the name. Then for the first parameter inside the paranthesis, type in the output. Then type in all the inputs (you can have as many inputs as you want). What is Instantiationlet's say inside your wardrobe, you have alot teddy bears. 🧸🧸🧸🧸 to uniquely identify each teddy bear, each teddy bear needs a name, like "Bob🧸", "Fred🧸", "Sam🧸". |

|

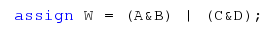

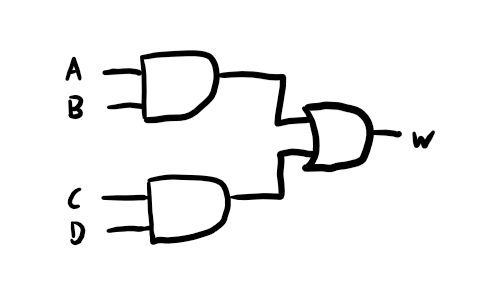

assignUse assign to quickly construct a logic gate structure note these logical operators

|

|

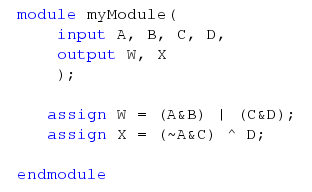

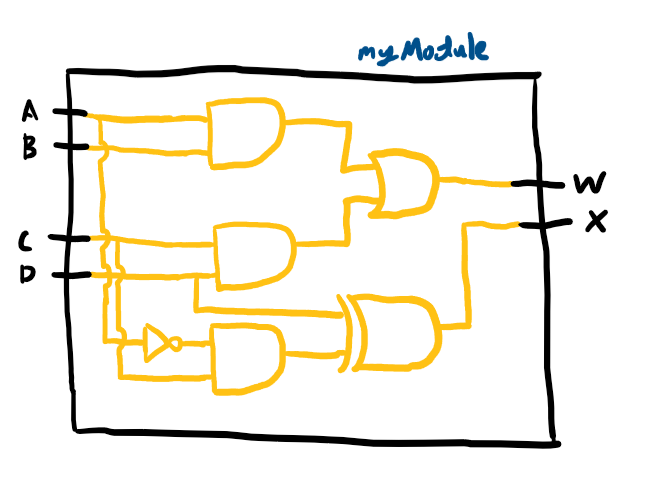

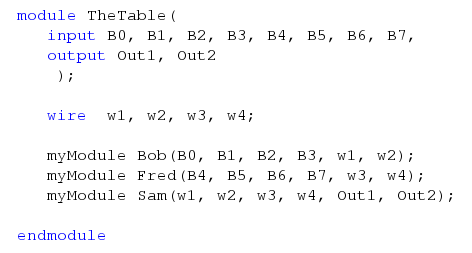

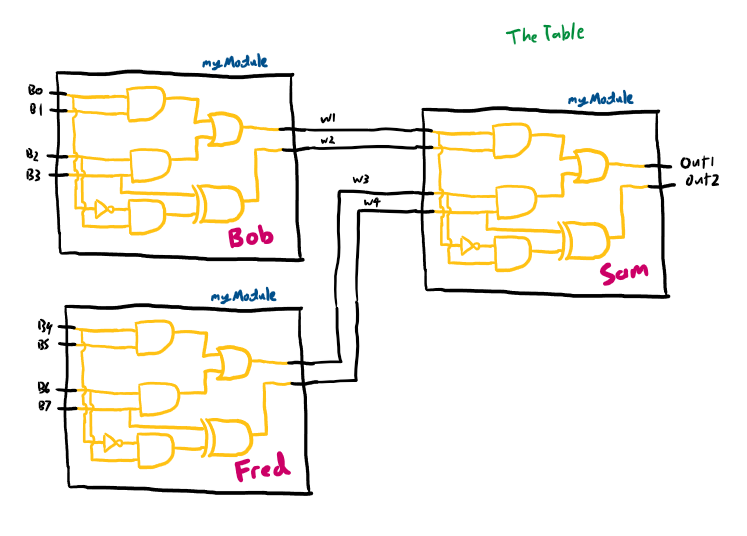

Custom modulesModule is an object that can be reused. Start by declaring your input and output in the paranthesis and giving your module a name. Inside the module, write whatever logic you want inside the module. By having this module, now you created this block which you can use in other logic circuits |

|

InstantiationIn verilog, each module needs a name such that the module finds itself a unique place in the hierarchy Following myModule from the previous section in module, we can instantiate by stating the module name, the instance name. And inside the paranthesis, enter all the wires corresponding to how you define the module inputs and outputs |

|